|

|

Overview of Current Research

|

Hardware Security & Trust

Security of electronic hardware, in particular,

integrated circuits (ICs), is rapidly becoming an important design, test, and validation concern with growing

number of attacks at different stages of IC life-cycle. Hardware Intellectual Property (IP) piracy and reverse

engineering efforts have emerged as major concerns for IP vendors and design houses. It has been critical develop

low-cost design techniques for preventing IP infringement at different stages of IP life-cycle. Nanoscape is presently

investigating netlist and register transfer level design solutions for hardware IP protection that ensures trust and

security for all parties involved in system design flow while not affecting end user experience. Another major security

concern for hardware is malicious alteration of a design in an untrusted foundry. Conventional test generation, application

and coverage determination do not directly apply to detect such alterations, commonly referred as hardware Trojan. At

Nanoscape, we are exploring novel solutions for post-silicon Trojan detection techniques as well as design methodology to

prevent Trojan insertion and/or facilitate Trojan detection. We have developed a key-based hardware obfuscation approach

to protect hardware IP against different forms of attacks. Research on hardware security at Nanoscape has resulted into

collaboration with Dr. Sandip

Ray, NXP Semiconductors on system on chip and platform security; with

Prof. Debdeep Mukhopadhyay, IIT Kharagpur, India, on emerging threat analysis in cryptographic chips; and with

Prof. Prabhat Mishra, University of Florida, USA on hardware IP trust. |

|

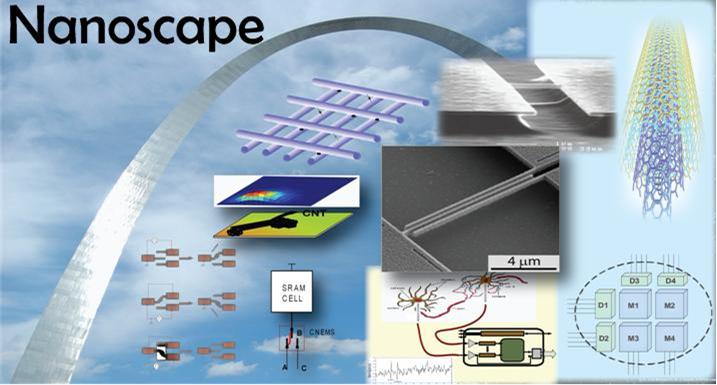

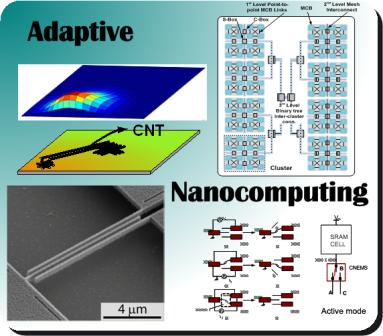

Adaptive Nanocomputing

While emerging nanodevices show promises in terms of terascale integration, ultra low-power operation or tera-hertz switching, system design with these devices involves some major challenges. At nanometer scale, these devices suffer from high defect rate and susceptibility to large parameter variations. We target developing model, architecture and circuit for adaptive nanocomputing, which address these challenges while taking advantage of the dense and regular structure of the nano-fabric. Research at Nanoscape has led to a novel memory based reconfigurable computing paradigm that leverages on the suitability of nanoscale devices, such as molecular crossbar, spin-torque random access memory or memristor to fabricate high-density two-dimensional memory array. Application of the nanocomputing model, architecture and circuit are also being investigated for specific nanotechnologies – such as a carbon nanotube based Nano-Electro-Mechanical System (NEMS) complementary switch and poly-SiC based NEMS switch suitable for high-temperature electronics (in collaboration with Prof. Mehran

Mehregany at Case). Collaborative research with Prof. Mehregany on harsh environment electronics using silicon carbide has been recently reported in several international news sites [Physorg] [NewScientist] [PhysicsWorld]. The work has also been featured in Nature Nanotechnology, Oct 2010 in its "Research Highlights" page. |

|

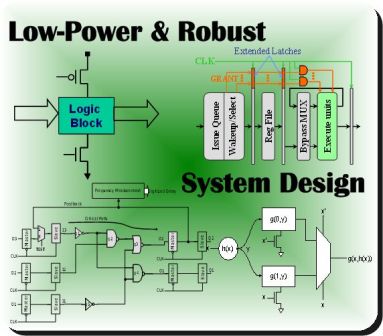

Low Power & Robust System Design

Power and robustness of operation have emerged as two

major concerns for digital design with nanoscaled CMOS. Low power design techniques such as voltage scaling,

dual-threshold voltage (Vth), power gating typically impose contradictory design requirements with respect to

robustness of a design. Nanoscape targets developing circuit-architecture level design methodology for low power

and variation tolerance, while minimizing the design overhead. Of particular importance is tolerance to process-induced

parameter variations as well as to time-dependent device degradations (in collaboration with Prof. Kaushik Roy

at Purdue University and Prof.

Saibal Mukhopadhyay at Georgia Tech) and healing of both logic and memory circuits with

minimal impact on power and performance. Research in Nanoscape has led to novel power gating solutions, in particular

dynamic supply gating (DSG) to save active leakage and switching power in datapath and control logic blocks. Architecture

level power saving techniques in microprocessors and robust low-cost processor cache design techniques are also explored. |

|

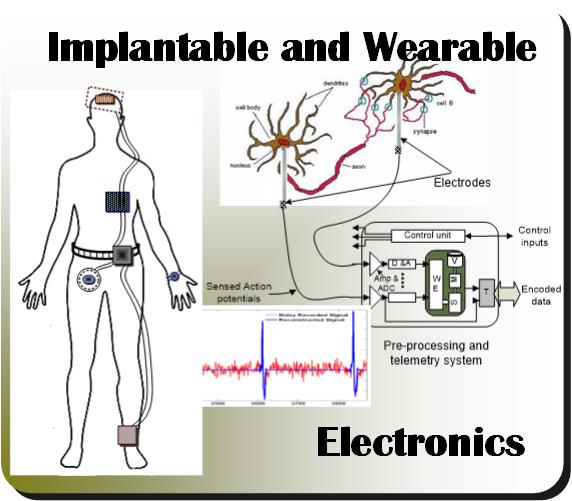

Implantable and Wearable Electronics For centuries, researchers and scientists around the globe have dreamed of understanding central nervous system and performing surgical interventions to manipulate its activity. With the advances in bio-MEMS and nanoelectronics, interpreting and engineering the activity of the central nervous system in terms of its communication with body parts are poised to make dramatic progress using miniaturized implantable biomedical microsystems. Such implantable microsystems require monitoring the activities of neural network at cellular level using arrays of micro-electrodes. In Nanoscape, research efforts are underway to develop efficient algorithms and hardware design techniques for performing spike detection, alignment and classification of the action potential signals from a large number of electrodes in an efficient manner as well as behaviorally meaningful neural pattern recognition (in collaboration with Prof. Hillel Chiel and Prof. Chris Zorman at Case). Moreover, analysis of pressure data and detection of important events from implantable bladder pressure sensors are also being investigated (in collaboration with Dr. Margot Damaser at Cleveland Clinic Foundation). Finally, research at Nanoscape lab also focuses on developing novel wearable systems for health monitoring and timely detection of onset of diseases including different forms of cancer. |